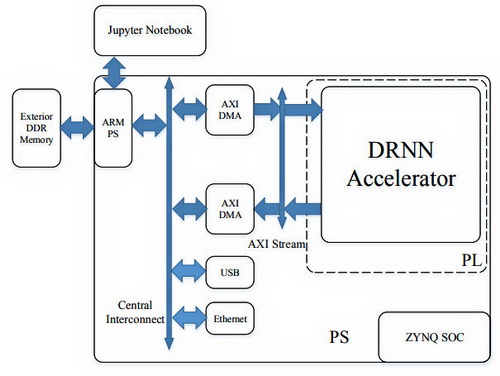

The latest proof points are the recently published papers by Yufeng Hao and Steven Quigley of the Department of Electrical, Electronic and Systems Engineering at the University of Birmingham, UK. The paper titled "Realizing a Deep Recurrent Neural Network Language Model on Xilinx FPGAs" introduces the use of the Python programming language to successfully implement and train a fixed-point-depth recursive neural network (DRNN); Theano mathematics library and multidimensional arrays; Open source based Python's PYNQ development environment; the Digilent PYNQ-Z1 development board and the system-on-chip SoC of the Xilinx Zynq Z-7020 on the PYNQ-Z1 board. The Zynq-7000 series is loaded with a dual-core ARM Cortex-A9 processor and 28nm Artix-7 or Kintex-7 programmable logic. Integrating the CPU, DSP and ASSP on a single chip, with key analysis and hardware acceleration capabilities and mixed-signal capabilities, excellent price-performance ratio and maximum design flexibility are also features. Using Python DRNN Hardware Acceleration Override (a Xilinx-proposed hardware library, using Python APIs to establish connections and exchange data in hardware logic and software), two collaborators use this design as an NLP (Natural Language Processing) application The processing throughput of 20GOPS (1 billion times per second) is achieved, which is 2.75 times to 70.5 times better than the earlier FPGA-based implementation.

ZGAR AZ Vape Pods 5.0S

ZGAR electronic cigarette uses high-tech R&D, food grade disposable pod device and high-quality raw material. All package designs are Original IP. Our designer team is from Hong Kong. We have very high requirements for product quality, flavors taste and packaging design. The E-liquid is imported, materials are food grade, and assembly plant is medical-grade dust-free workshops.

From production to packaging, the whole system of tracking, efficient and orderly process, achieving daily efficient output. WEIKA pays attention to the details of each process control. The first class dust-free production workshop has passed the GMP food and drug production standard certification, ensuring quality and safety. We choose the products with a traceability system, which can not only effectively track and trace all kinds of data, but also ensure good product quality.

We offer best price, high quality Pods, Pods Touch Screen, Empty Pod System, Pod Vape, Disposable Pod device, E-cigar, Vape Pods to all over the world.

Much Better Vaping Experience!

ZGAR AZ Pods 5.0S Pods,ZGAR AZ Vape Pods 5.0S,ZGAR AZ Vape Pods 5.0S Pod System Vape,ZGAR AZ Vape Pods 5.0S Disposable Pod Vape Systems ZGAR INTERNATIONAL(HK)CO., LIMITED , https://www.zgarvapepen.com

This paper includes a lot of in-depth technical details, but this sentence summarizes the reasons for this blog post: "More importantly, we show the joint application of software and hardware design and simulation process in the field of neural networks." Considering that the price of the PYNQ-Z1 development board is 229 US dollars, this statement is completely correct.

Disclaimer: This article is sourced from the Xilinx Xcell Daily Blog. It was compiled by the Xilinx Chinese community. Please indicate the author, source, and original link. https://forums.xilinx.com/t5/Xcell-Daily-Blog/U- of-Birmingham-team-develops-fixed-point-Deep-Recurrent-Neural/ba-p/805717

Programmable logic (PLD) is generated by a general-purpose integrated circuit. The logic function is determined according to the user's programming of the device. The user can program the digital system to integrate in the PLD. After years of development, programmable logic devices have evolved from programmable logic array devices (PLDs) in the 1970s to field-programmable array logic (FPGA) with tens of millions of gates. With the development of artificial intelligence research, FPGAs have been developed. The parallelism has been applied in some real-time neural network computing tasks. Since implementing floating-point numbers on an FPGA consumes a lot of hardware resources, while the accuracy of fixed-point numbers is limited, convergence can still be guaranteed for different applications by selecting an appropriate word-length precision, and the speed is faster and the resources are less expensive than floating-point numbers. It has made it ideal for embedded AI and machine learning applications. The Vivado Design Suite provides new ways for the next generation of ultra-efficient C/C++ and IP-based designs. With the new set of ultra-fast and efficient design methods, users can achieve 10-15 times more efficiency. Vivado HLS supports ISE and Vivado design environments and can accelerate IP creation by integrating C, C++, and SystemC standards into Xilinx's programmable devices without the need to create RTL models.